## "SDR vs. Legacy Radio - which is better?"

(presented at APDXC 2016, Osaka, Japan)

### Adam Farson VA7OJ/AB4OJ

Copyright © 2016 A. Farson VA7OJ/AB4OJ

### The ITU-R definition of Software Defined Radio Recommendation SM.2152-0 Section 1

"Software-defined radio (SDR): A radio transmitter and/or receiver employing a technology that allows the RF operating parameters including, but not limited to, frequency range, modulation type, or output power to be set or altered by software, excluding changes to operating parameters which occur during the normal pre-installed and predetermined operation of a radio according to a system specification or standard."

# Scope of presentation

- SDR and cognitive radio technology are rapidly displacing legacy radio architecture in critical military, government and commercial applications.

SDR solutions are developing and also making a strong showing in the amateur radio service.

- 2. Several new OEM's, as well as a strong open-source group, are building SDR transceivers and receivers rivalling and even surpassing legacy radio equipment. Established manufacturers are transitioning from legacy to SDR designs.

- 3. This presentation will explore the relative merits of SDR and legacy radios, and the issues peculiar to each type, from the radio amateur's perspective.

- 4. Only two radio technologies will be considered here: the legacy superhet with a DSP IF chain and the direct-sampling/DUC\* SDR. It is assumed that the serious radio amateur will choose one or the other of these, or both.

- 5. As both topologies embody such familiar DSP-based features as noise reduction, noise blanking, notch filters, PBT, speech compression etc., these facilities will not be discussed in detail here.

\* DUC = digital up-conversion

## Abbreviations

#### SDR has created many new ones!

- ADC: Analogue/Digital Converter

- DAC: Digital/Analogue Converter

- dBFS: dB relative to full scale (clip level)

- DDC: Digital Down-Converter, Digital Down-Conversion

- DSP: Digital Signal Processor, Digital Signal Processing

- DUC: Digital Up-Converter, Digital Up-Conversion

- FFT: Fast Fourier Transform

- FPGA: Field-Programmable Gate Array

- HPA: high-power amplifier

- LNA: low-noise amplifier

- NCO: Numerically Controlled oscillator (a DDS, or digital direct synthesiser, with digital output)

- NF: Noise Figure

- PIM: passive intermodulation (in magnetics, crystal resonators, dielectrics)

- PIN (Positive/Intrinsic/Negative) Diode: Used as voltage-controlled attenuator or switch

- SDR: Software-Defined Radio

### Outline of legacy vs. SDR topology

- Legacy superheterodyne with IF-level DSP

- A DSP chain consisting of an ADC, DSP and DAC constitutes the RX analogue final IF/demodulator chain and the TX analogue modulator/1st IF chain. In a restricted sense, this DSP chain is a "mini-SDR" operating at the IF.

- Direct-sampling/digital up-conversion SDR

- Receiver: ADC sampling at RF, digital down-converter DDC (decimator) with numericallycontrolled oscillator NCO, DSP, baseband DAC.

- Transmitter: Audio ADC, DSP, digital up-converter DUC with NCO, RF DAC, RF PA chain.

- The NCO is "tuned" to the operating frequency. The DDC, DUC and NCO functions are usually incorporated into a Field-Programmable Gate Array (FPGA). Some designers are studying the use of a Graphics Processing Unit (GPU) for the functions normally resident in the FPGA.

- Note: RF preselector/preamp/attenuator block, RX/TX audio chains and TX RF PA chain are common elements in both the above radio architectures.

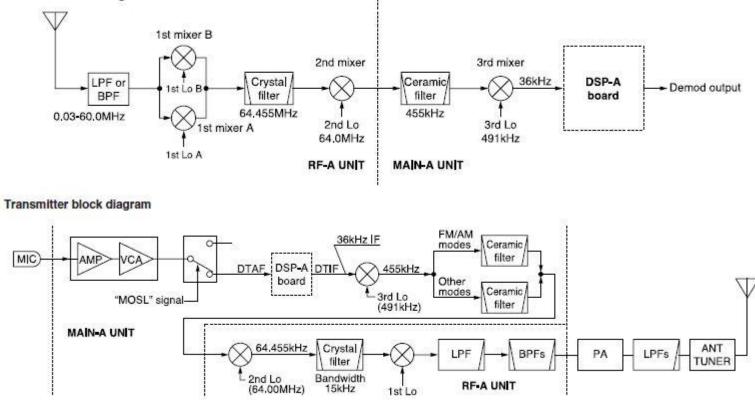

## **Typical Legacy HF Transceiver**

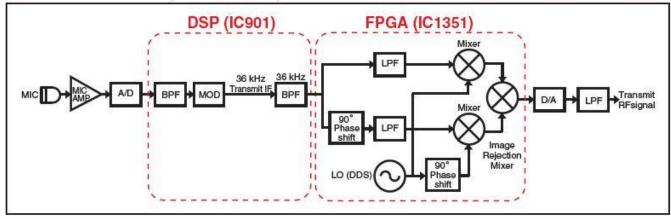

with IF-level DSP (courtesy Icom Inc.)

**Receiver block diagram**

- In a direct-sampling SDR RX, the ADC and FPGA replace all the blocks between the LPF/BPF and the DSP. Input.

- In a DUC TX, the FPGA and DAC replace all the blocks between the DSP output and the exciter LPF/BPF group.

- The DSP, with its input ADC and output DAC, is in effect a "mini-SDR" operating at the 36 kHz IF.

### Legacy receiver topology with I/Q 2<sup>nd</sup> mixer 64.455 MHz -> 36 kHz in 1 step

Fig.1 Receiver block diagram

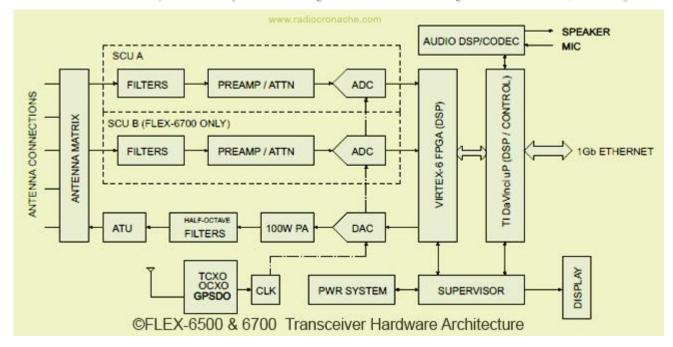

# Direct-Sampling/DUC SDR

FLEX-6500/6700 (courtesy FlexRadio Systems & IØGEJ)

- In the Flex-6000 series, all signal processing takes place within the radio. The PC (or "Maestro" control head) connected to the Ethernet port is used for user interface, display and control only..

- Other SDR designs allocate major signal-processing tasks to the connected PC (e.g. Apache Labs ANAN series). Here, the payload link between radio and PC is at baseband.

- The received signal is digitised in the ADC and remains in the digital domain until it is decoded to audio by the CODEC.

- The CODEC digitises the modulating signal on transmit. The signal remains digital until it is decoded to RF drive in the DAC.

#### FPGA BLOCK DIAGRAM (Transmit circuits)

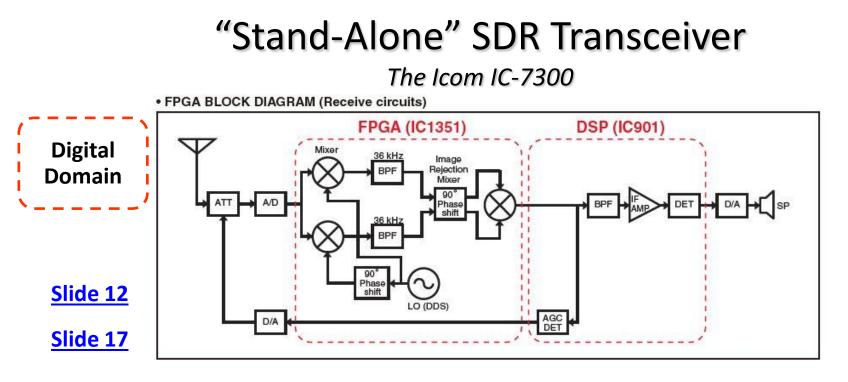

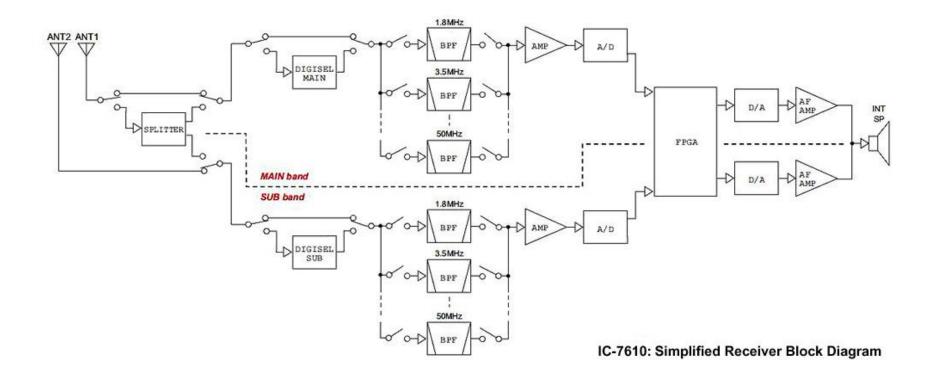

### The Icom IC-7610

#### Receiver Block Diagram

### **SDR Architectural Advantages**

- Dramatic simplification of block diagram & signal paths vs. legacy designs

- Elimination of legacy subsystems (and their attendant impairments)

- Mixers (IMD, noise, spurs, images)

- Analogue local oscillators (phase noise/reciprocal mixing, spurs)

- IF "roofing" filters (PIM, phase distortion, insertion loss, IF leakage)

- Note: An anti-aliasing filter is required to suppress aliasing response.

- Digitisation of the payload signal at the earliest stage

- Signal management entirely in digital domain

- No added noise or distortion between ADC and DAC

- Software-defined signal processing greatly facilitates addition of new modes, protocols, features etc.

- o Cost-effective customisation to meet needs of different user communities

- o Dithering reduces ADC IMD at very slight cost to noise floor

#### o Simplified maintenance

- Hardware alignment points (trimmers etc.) virtually eliminated

- o Adjustment/calibration parameters accessible via secured software menus

- o Easily configurable interfaces to other equipment

- Greatly reduced component count

- o reduction in cabinet size, weight, number of PCB modules

- o significant reliability improvement & cost reduction

- o Potential reduction in standby power consumption

### **SDR Dynamic Range Considerations**

ADC Clip Level and the Input Power Limit

- The ADC clip level (the input level at which the output is all ones) sets an absolute limit on the signal level which can be applied to the input. At the clip level, the ADC stops encoding the analogue input.

- A typical ADC clip level (measured at the antenna input) is -3 dBm (S9 + 70 dB). Thus, the ADC will clip when the total instantaneous power of all applied signals is -3 dBm.

- The ADC is exposed to all RF signals in the RF passband. The passband width is limited by a preselector (BPF) which can be switched out in some designs for wideband reception. Certain SDR models are not fitted with preselectors.

- If all the applied signals were equal in amplitude and phase, the clip level would decrease by  $10 \log_{10}$  (number of signals), e.g. (-3-18) = -21 dBm for 64 signals.

- Statistically, though, this is seldom if ever the case. This is why a direct-sampling receiver with an ADC at RF works as well as it does.

- The optimum operating point for a direct-sampling SDR receiver is where the band noise is at or just above the receiver's noise floor, to maximise ADC dynamic range.

### SDR Dynamic Range Considerations AGC and Front-End Gain Management

- The input power limit imposed by ADC clipping requires a different approach to AGC design in a direct-sampling SDR as opposed to a legacy receiver.

- In a <u>legacy</u> superhet/IF-DSP receiver, the AGC levels average audio output over a wide range of RF input levels, and prevents overload of downstream mixers and IF stages.

- In a direct-sampling <u>SDR</u>, the AGC can also adjust the ADC input level via a voltagecontrolled RF attenuator to keep the ADC below clip level when a strong signal is present in the detection bandwidth. (Some SDR's have an ADC clip indicator.)

- Strong signals outside the detection channel can drive the ADC into clipping.

- The operator can also set the ADC input level via a manual RF gain control to keep the ADC below clip level. If the front end has sufficient gain reserve, sensitivity will not be excessively degraded.

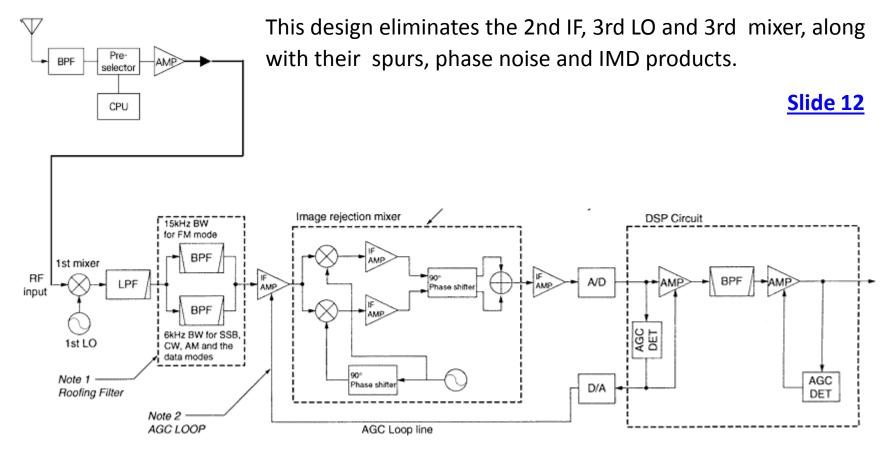

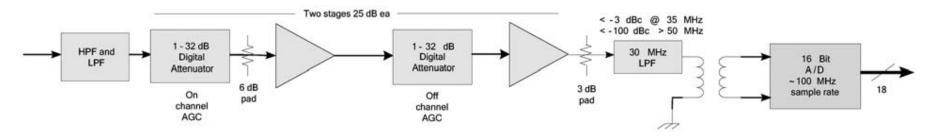

- One <u>SDR design</u> has in-channel and out-of-channel AGC loops to keep the ADC within its linear range whilst preserving the front-end noise figure in the presence of strong out-of-band signals.

## SDR Front End w/2 AGC Loops

**Slide 12**

- Off-channel AGC adjusts input to 2<sup>nd</sup> stage (ADC driver).

- On-channel AGC adjusts input to 1<sup>st</sup> stage (preamp).

- There is no provision for turning off either AGC loop.

### **SDR Dynamic Range Considerations**

#### ADC Noise Floor and Process Gain

- The noise floor of a "noiseless" 16-bit ADC is  $(16 * 6) + 1.76 \approx 96.8$  dBFS, measured at a bandwidth B =  $f_s/2$  (one-half the sampling frequency).

- In the "real world", the noise floor of a typical 16-bit ADC (LTC2208-16) is 78 dBFS at B = 65 MHz (sampling at 130 MHz). Thus, effective number of bits (ENOB) = (78-1.76)/6 ≈ 12.7.

- A 14-bit ADC (LTC2208-14) has a 77 dBFS noise floor. Here, ENOB = (77.1-1.76)/6 = 12.55. Not much difference!

- This 78 dB dynamic range of at B = 65 MHz looks unimpressive. But now we bring in the "magic" of process gain.

- The DDC (digital down-converter), usually in the FPGA, scales down the channel bandwidth by a process known as <u>decimation</u>. If the final detection bandwidth is 500 Hz, the scaling factor is (65 \* 10<sup>6</sup>)/500 = 1.3 \* 10<sup>5</sup>.

- Process gain =  $10 \log_{10}(1.3 * 10^5) = 51 \text{ dB}$ . Adding this to the 78 dB noise floor, we get a calculated instantaneous dynamic range of 129 dB!

- Of course this will fall apart if all the applied signals are equal in amplitude and phase. But in practice, that seldom if ever happens.

### MDS – IMD – Dither

- For the LTC2208 ADC, NF  $\approx$  23 dB. Thus, MDS = -124 dBm for B = 500 Hz (CW).

- A differential ADC driver (e.g. LTC6401-20) has 20 dB gain and 6 dB NF. The calculated NF of the LTC6401 driving the LTC2208 is 8 dB. Allowing 5 dB insertion loss for the preselector, system NF ≈ 13 dB. Thus, system MDS = 134 dBm . This is comparable to the MDS of a legacy transceiver.

- On 21 MHz and above, a low-noise RF preamp can be added ahead of the ADC driver to lower the NF even further.

- The LTC6401 IMD spec ≈ -100 dBc, so the ADC driver should not significantly degrade the ADC's IMD performance.

- Dithering is an on-chip function on many ADC types (including the LTC2208). When active, dithering de-correlates IMD products generated in the ADC. It can lower IMD levels significantly, at the cost of a slight increase in NF.

- Many direct-sampling SDR receivers feature a user-accessible Dither switch. Nothing comparable exists in any legacy radio.

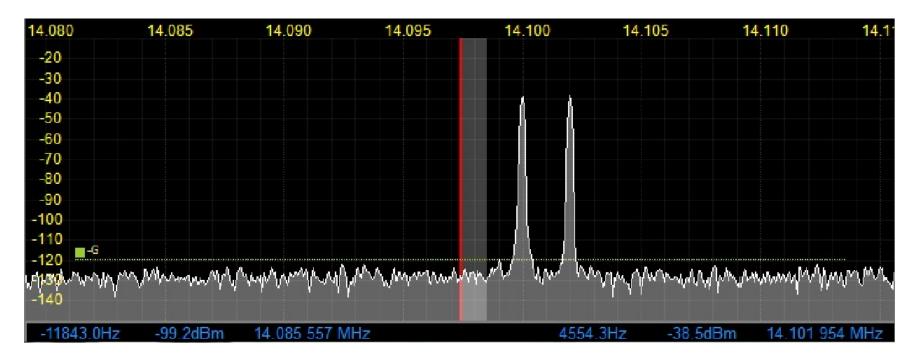

### Spectrum Scope & Signal Level Meter

Example: PowerSDR OpenHPSDR mRX on ANAN-200D

- The scope is an FFT, which samples an entire band in one operation.

- Y-axis amplitude values (and those of the signal level meter) are derived from the ADC digital output and are thus inherently accurate.

- X-axis frequency value is derived from the NCO (FPGA) to ensure accuracy.

- With the preselector out, the scope can display the receiver's entire tuning range.

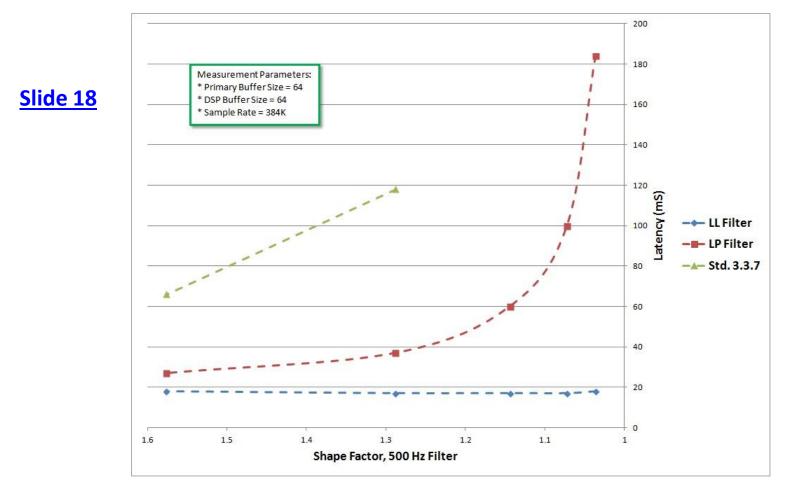

### Latency Issues

- Latency is the combined delay between an input (or command) and the desired output.

- In a radio receiver or transmitter, latency is the respective transit time of a signal from input (antenna or audio/keying source) to output (audio output or antenna).

- Contributors to latency include active circuits and filters in the signal path.

- In a purely analogue radio, crystal or mechanical filters are the largest contributors. Still, total latency is 1-2 ms or less.

- In a legacy radio with IF-level DSP, the ADC-DSP-DAC transit time is the most significant cause of delay. Narrow DSP filters with steep skirts (low shape factors) can increase latency significantly. Even so, typical latency is 15-20 ms.

- Direct-sampling/DUC SDR's exhibit latency ranging from less than 5 ms to more than 400 ms. One popular model has 160-165 ms receive latency.

- The Icom <u>IC-7300</u> "stand-alone" SDR transceiver has receive latency in the 3.7 -16 ms range (highest values with narrow DSP filters) and 4 ms transmit latency. This compares well with legacy superhet/DSP radios.

### Latency Mitigation

- Latency (signal transit time from RF input to audio output) in an SDR is a function of real-time processing power, and is directly affected by DSP filter parameters.

- Latency is of critical importance in high-speed CW operation (especially QSK), and also in the digital modes.

- Latency > 100 ms can also degrade voice operation, especially fast back-&-forth with VOX, and can render the Monitor function almost unusable.

- A compromise must be struck between filter shape factor and latency.

- The <u>OpenHPSDR</u> group has made remarkable strides in this area, reducing receive latency to less than 20 ms.

- DSP transit time, whether in an internal DSP chipset or an external computer, also contributes to latency. This aspect can be addressed by code optimisation and use of a fast DSP or computer.

### **Typical Filter Shape Factor/Latency Curves**

#### PSDR OpenHPSDR mRX v3.3.7

LL: Low Latency. LP: Linear Phase. LP is provided as a user option. Std. 3.3.7 does not have these options.

### **Transmitter Considerations**

- A DUC (digital up-converting) SDR transmitter has several significant advantages over a legacy transmitter:

- 1. The audio/baseband signal leaving the audio ADC or codec remains in the digital domain until it leaves the DAC as RF drive to the PA chain. Thus, signal processing adds no noise or distortion to the signal.

- 2. As the ADC and DAC clocks are the primary phase-noise contributors, a design with lownoise clocks can almost eliminate transmitted phase noise from the transmitted signal.

- 3. The removal of mixers & LO's eliminates spurs and phase noise from these sources.

- 4. Transmit latency in CW mode can be greatly reduced by keying the carrier in the FPGA rather than in the DSP (or external PC). This greatly improves QSK operation.

- 5. Analogue IF filters, with their potential for phase distortion, are eliminated.

- 6. The DUC exciter topology facilitates the inclusion of HPA linearisation schemes such as adaptive predistortion (example: PureSignal).

- 7. The parts count of a DUC transmitter is much lower than that of most legacy transmitter architectures.

- 8. A DUC transmitter has far fewer alignment points than a legacy design.

### **SDR Operational Features**

- A wideband FFT spectrum scope displaying the RF band present at the ADC input can be configured to display either a narrow segment, an entire amateur band or the full RF bandwidth of the receiver (with preselector bypassed). The scope will also display the spectrum of the transmitted signal.

- In some SDR designs, two independent front ends, each with its own preselector and gain management tools, support diversity reception, wide/crossband split and even full-duplex operation with relative ease.

- SDR implementations with an Ethernet baseband interface to a PC facilitate addition of new modes, experimental signal-processing software development and virtual interfaces to popular amateur radio software (contesting/logging programs etc.)

- Although an SDR which is "stand-alone" or uses the PC only as a control surface is essentially a closed system, many of these designs also allow virtual connections to amateur radio software.

- Direct-sampling SDR's perform best with gain management based on a good understanding of the relationship between signal strength, band noise and MDS.

### "So which is better – an SDR or a legacy radio"?

- The individual operator's specific needs will determine the response to this question. There is no "one-size-fits-all" answer.

- SDR can offer clear advantages over legacy architecture in terms of overall performance, design simplicity, versatility, reliability and cost.

- Nonetheless, some top-ranking legacy HF transceivers perform superbly in brutal RF environments, both in amateur service and in demanding mil/gov and commercial usage.

- In choosing between an SDR requiring a PC (either for signal processing and control or for control only) and a stand-alone "knobbed SDR", purchasers should be guided by their personal preferences.

- Radio amateurs who have been comfortable with legacy radios may find that a "stand-alone" SDR meets their needs, whilst providing a refreshing uptick in performance and capability.

### **References for further study**

- 1. <u>http://www.itu.int/pub/R-REP-SM.2152-2009</u>

- 2. <u>http://tinyurl.com/sdr-debunk</u>

- 3. <u>http://openhpsdr.org/</u>

- 4. <u>http://www.ab4oj.com/sdr/sdrtest2.pdf</u>

- 5. <u>http://www.ab4oj.com/icom/ic7300/main.html</u>